x86芯片定制,Ethercat芯片定制

X86平台

我们的研发工程师已经积累了非常丰富的主板、整机设计经验,对接您的产品规格场景需求,快速交付样机,包含主板、BOX整机、平板电脑、CPCI等形态产品。降本、长生命周期、快速交付、及时响应是我们的优势。

® 客制化集成电路服务

弹性服务、完整方案

客制化指令集整合

系统级思维设计

凭借累积多年工业计算机硬件平台导入量产技术实力,提供高弹性的芯片设计以及芯片量产服务并以系统级思维为客户设计解决方案,帮助客户提升竞争力。

Development Process

XMTECH® ASIC提供完整服务和产业应用方案;第一在设计服务量产面,从设计、生产制造到后端封装测试,®提供量身订制的客制化服务解决方案;在应用面,依产业应用不同,例如:嵌入式应用、工业自动化产业、云端物联网产业…等,®提供硬件规格设计建议并以系统角度求得硬件与软件相互契合,为客户提供完善的硬件规格配置与设计;在功能验证面,®阶段式提供不同验证方法论以强化功能验证完整度,在客制化项目面,从CPU到各项周边装置,从标准接口到特殊规格,丰富的功能提供,帮助客户设计多元应用芯片;在制程面,从成熟制程到先进制程,®会视客户系统需求及成本效益考虑,以最适制程达到最佳效能。®提供具弹性,最完整的解决方案协助客户强化产品、巩固市场。

®客制化研发流程以系统角度帮客户打造最符合成本效益之客制化芯片。

ASIC Service Flow

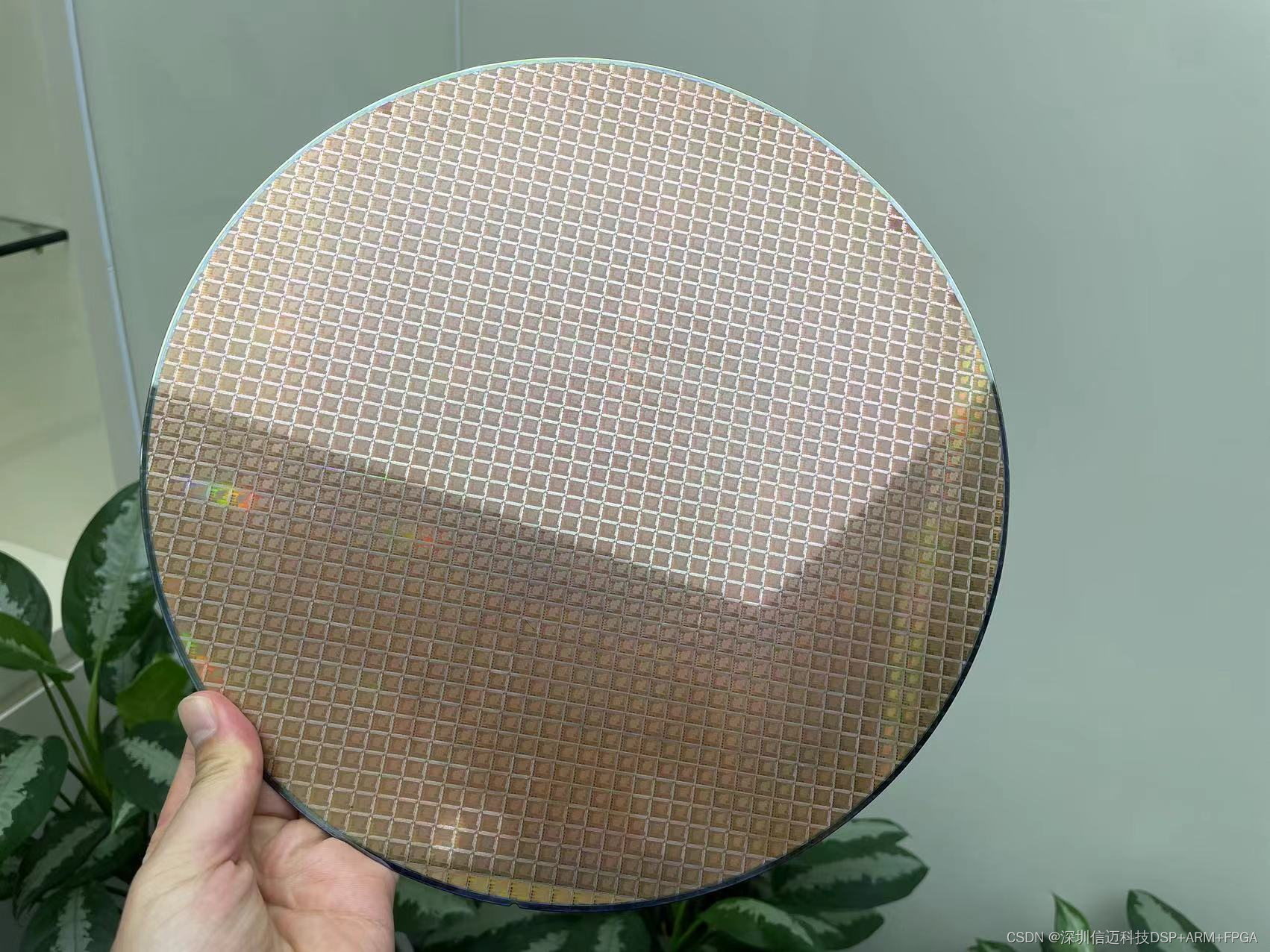

在规格订制阶段与客户讨论产品应用,规格需求并提供符合需求及成本的设计建议;在芯片设计时间搭配FPGA测试板仿真评估效能并做系统优化;在物理层设计时间运用计算机辅助软件评估功耗及效能并做优化;在功能验证阶段,阶段式的验证方法提供,加强验证完整度,减少验证响应时间以利缩短研发时程;在芯片量产阶段包括晶圆生产服务到芯片封装测试,协助客户优化量产程序,降低量产风险。®在各个阶段皆会与客户讨论,聆听客户意见并提供最符合成本与效能的解决方案。

IP Service

Design Specification

- RISC Architecture

- Synchronous Design

- Static Design

- Synthesizable

- Silicon proved (0~66 MHz at 0.5um process)

Key features

|

|

Deliverable

- Product Data Specification

- RTL code in Verilog format

- Pipeline Diagram

- Synthesis Script file

- Function Test Pattern in Verilog format

Application

DSC,CF Card, Pattern Recognition, LCD Monitor Controller, USB Device Controller, Scanner Controller, MP3 Controller, Modem Controller, Voice Recognition

概述

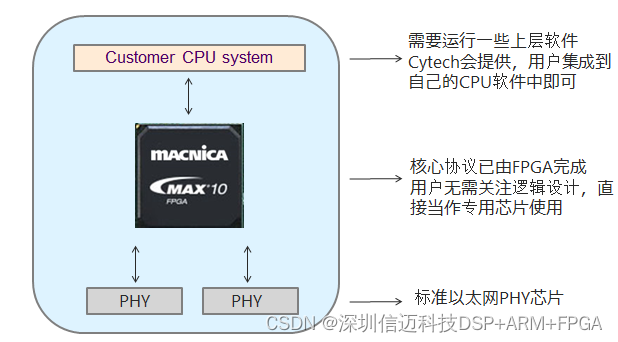

EtherCAT商业主站和开源主站,都是使用软件的方法实现主站功能,主站的性能很大程度上取决于PC的性能和操作系统的实时性。而信迈将EtherCAT的协议层用FPGA逻辑实现,预先编程好,客户只需当作专用芯片使用。

EtherCAT max10芯片实现了标准的EtherCAT主站协议,采用标准的通用并行总线接口,可以连接任何CPU,并对芯片进行控制。支持ARM处理器或者x86处理器平台。提供参考软件代码,API函数,XML文件初始化系统等软件。可用于任何标准的 EtherCAT 电机、IO设备的控制。

特点

⦁ 支持ARM处理器上裸机程序运行EtherCAT主站,无需操作系统;

⦁ 支持x86处理器,PCIe接口,提供Linux(withXenomai实时内核)下的驱动和应用程序的参考代码;

⦁ 友好的系统调试界面;

⦁ CPU负担小,无论高端或低端处理器,都能快速实现高实时性能的EtherCAT主站通信;

⦁ 主站与从站间的同步性能强,同步时间的抖动远小于1us(4轴实测50ns);

⦁ 循环周期短,可以轻松实现31.25us的通信周期(可实现4轴62.5us的循环周期);

⦁ 通过XML文件轻松配置系统,可接从站数量多

性能对比